Design代码中的计数器设置是因为我的开发板的时钟是100MHZ的,也就是1秒完成了100_000_000次时钟信号,所以我设置计数器为100_000_000次 。

也就是说,我让流水灯的变化周期为1 s 。

counter == 32'd100_000_000

文章插图

代码

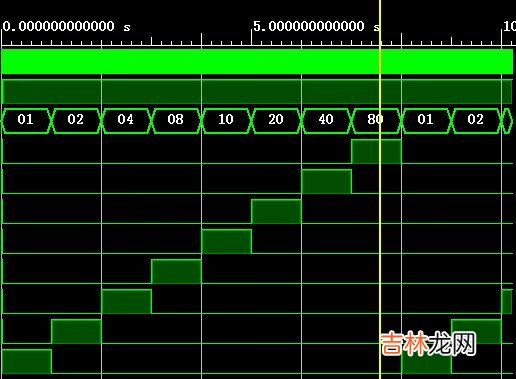

`timescale 1ns / 1psmodule flow_led(clk,reset,led);input clk;input reset;output [7:0] led;reg [7:0] led;reg [31:0] counter;reg [1:0] state; always @(posedge clk or negedge reset)beginif(!reset)begincounter <= 32'd0;endelse if ( counter == 32'd100_000_000) //change Tbegincounter <= 32'd0;endelsebegincounter <= counter + 32'd1;endendalways @(posedge clk or negedge reset)beginif(!reset)beginstate <= 8'd0;endelse if( counter == 32'd0 )beginstate <= 1'd1;endelsebeginstate <= 1'd0;endendalways @(posedge clk or negedge reset)beginif(!reset)beginled <= 8'b1111_1111;endelsebeginif(state == 1'd1)beginif(led == 8'b1111_1111)beginled <= 8'b0000_0001;endelse if(led == 8'b1000_0000)beginled <= 8'b0000_0001;endelsebeginled <= led << 1'b1;endendendendendmoduleSimulation若在波形仿真中,我们想让与模拟的时钟信号也是100MHZ,让流水灯的周期也为1s,那样的话仿真是跑不完的 。所以我们先修改刚刚的计数周期:

counter == 32'd1_000_000仿真中让时钟周期为1000 ns

【Vivado_8位流水灯】

parameter T=1000;这样就可以很轻松的看到流水灯全周期的波形图了 。

代码

`timescale 1ns/1nsmodule sim_dev1();parameter T=1000;reg clk;reg reset;wire [7:0] led;initialbeginclk=1'b0;reset=1'b0;#(T+1) reset=1'b1;endalways #(T/2) clk=~clk;flow_led u1(.clk(clk),.reset(reset),.led(led));endmodule波形图

文章插图

参考资料

- FPGA_VIVADO_verilog_八个流水灯_1

- vivado 对高阻z和不定态x信号的处理

- vivado波形仿真中运行时间的设置以及时长的测量方法

经验总结扩展阅读

- 房贷月供4000要多少收入流水 房贷月供占工资比例多少适合

- 18位身份证格式怎么写

- 我用情付诸流水歌词是什么意思

- 黄山高山流水有哪几种

- 国庆节歇后语

- 珍爱生命的名言警句

- 西游记去世演员18位?

- 银行流水是什么没有银行流水怎么办?

- 银行流水是什么?

- 车贷需要多少银行流水?