* 参考spec:the-compute-architecture-of-intel-processor-graphics-gen9-v1d0.pdf

SOC 架构Gen9 架构是早期用在igpu 中的 , igpu 集成在在整个cpu 的base die上 。Gen 9 是一个非常经典的架构 , 其中的设计思路一直沿用到Gen11 Gen12.5. 即使是最近两年Intel 新发布的dgpu , SG1( 内部代号DG1),ARC 系列显卡(内部代号DG2 , 2022) , Flex GPU 系列(内部代号ATSM).其核心架构思路都是承接于Gen9. 无非是增加了更多的EU (执行单元)或者一些media , render的硬件 。

- Architecture components layout for an Intel Core i7 processor 6700K for desktop systems.

文章插图

- Intel Processor Graphics Gen9 为igpu的架构 。接下里从大到小介绍 。

文章插图

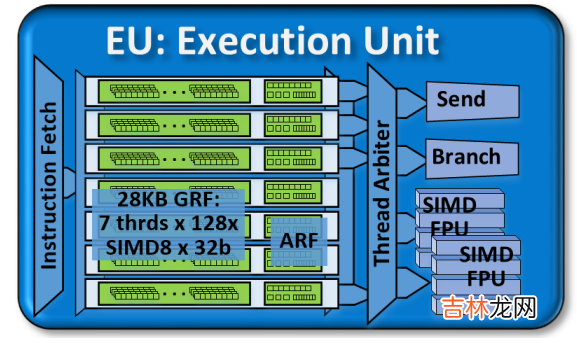

EU:【Intel GPU Gen 9 架构】EU 是最终指令执行的单元 , 但EU 不是最小的执行颗粒度 。EU 执行SIMD 指令 , 也就是单指令多数据 。

- 一个EU 包含7 个线程(Threads) , 这个线程是物理层面上的 , 不是软件模拟出来的 。每个threads 对应一系列的 128 SIMD-8 32bit 的寄存器 , 俗称GRF. 这样可以保证每个thread 都有单独取数据执行的能力 。

- 但是一个EU 取数执行的过程中 , 单个时钟周期只能并发四个指令 , 也就是对应两个FPU 单元 , Send 以及 分支预测 。FPU 相当于ALU (这是最终计算数据的地方) , 这里支持SIMD. 可以同时计算多个GRF 中的数据 。

文章插图

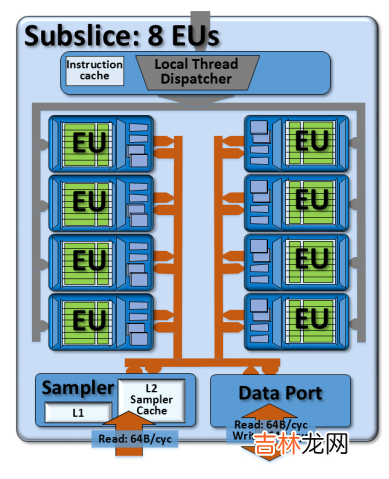

Subslice

- 8 个EUs 组成一个Subslice , 在这个Sublice 中有 local Thread Dispather 和 指令cache (Instruction Cache) , 用于把把指令丢到空闲的EU 上去执行

- 包含一个Sampler (两级缓存结构 L1 L2 cache), Sampler 主要存储的是 图片数据 , 当需要EU 进行渲染图片数据时 (平移 , 裁剪 , 旋转 , 映射) , Eu 的send 会发出取数据的指令 , 由于图片数据需要快速导入 , 如果直接从L3 cache 读取就太慢了 , sampler 主要缓存需要渲染的图像 。

- Data Port 负责从L3 cache 读取数据 。

文章插图

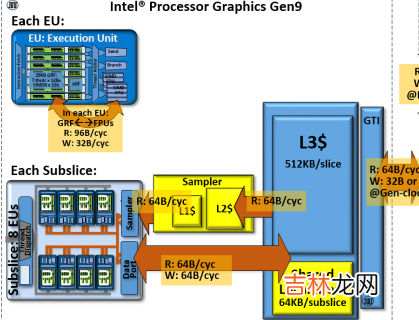

Slice:

- 每个slice 包含8 个 Subslices , 共计24 个EUs , 还有一个很大的L3 Data Cache 。

- 同样也包含global Thread Dispatcher 和 instruction Cache , 用来分配任务以及缓存指令

- Fixed function Units 这里主要是用于Render (图片渲染)的硬件电路 , Render 也是一个很大的topic , 需要单独介绍

- L3 Cache 用于存储GDDR 的数据 , 在Gen9 中 , SLM (shared Local Memory)是L3 中的一部分 , 在最新的Gen12 中 , SLM 与L3 分开 , 有单独的SLM 存储单元

文章插图

Memory 以及与Opencl 的内存模型关系

- GPU 一般通过GTI 硬件接口与外部存储相连接 , 当然在最新的GPU 架构中也出现了HBM 传输结构 , 实现GDDR 与GPU 的高速互联

文章插图

- PE1 PE M 是对应每个workitm , 应该是对应一个EU 的每一个thread 。这里的Private memory 就是每个Thread 的GRF.

经验总结扩展阅读

- 现代GPGPU 架构汇总

- 生成器函数 javascript异步编程之generator与asnyc/await语法糖

- 0基础90分钟会用PS——GenJi笔记

- ndarray numpy和tensor(GPU上的numpy)速查

- python3使用mutagen进行音频元数据处理

- [C#]SourceGenerator实战: 对任意对象使用await吧!!!

- 谷歌新AI系统Imagen有点强,输入文本就能生成逼真的图像

- 简单好记的微信号 augenstern什么意思

- tensorflow-gpu版本安装及深度神经网络训练与cpu版本对比

- AlexNet-文献阅读笔记