我们介绍了3D-NAND闪存引入的背景 , 应该可以大致了解三星V-NAND结构的含义 。本篇文章 , 我们就继续来详细的了解一下V-NAND的内容 。先通过具体参数的对比 , 感受一下V-NAND的优势:

从上表中 , 我们可以看到 , 与2D平面闪存相比 , V-NAND垂直结构的闪存优势很显著 , 主要集中在两点:

1. 容量增加:每个储存块(block)中的页数增加2倍 , 每个储存块(block)中可以包含的字节数 , 由1024K Bytes增加到了3*1024K Bytes. 字节数的增加 , 代表中储存容量的增大;

2. 性能提升:V-NAND的每个页的写入时间为0.6ms , 而平面NAND中的页写入时间是2ms, V-NAND足足快了1.4ms, 时间就是生命呀 。针对随机读方面 , V-NAND和平面NAND只相差3us, 处于同一水平 。在储存块(block)擦除方面 , V-NAND比平面NAND快了1ms.

上篇文章中 , 我们提到了在2D平面NAND中 , 随着制程进入20nm以下 , 不一样储存单元cell之间的相互相扰效应越来越严重 , 为了减少干扰效应 , 三星在V-NAND中引入了电荷陷阱(Charge Trap Flash, CTF)的概念 , 目的就是尽可能的消除储存单元之间的干扰 。

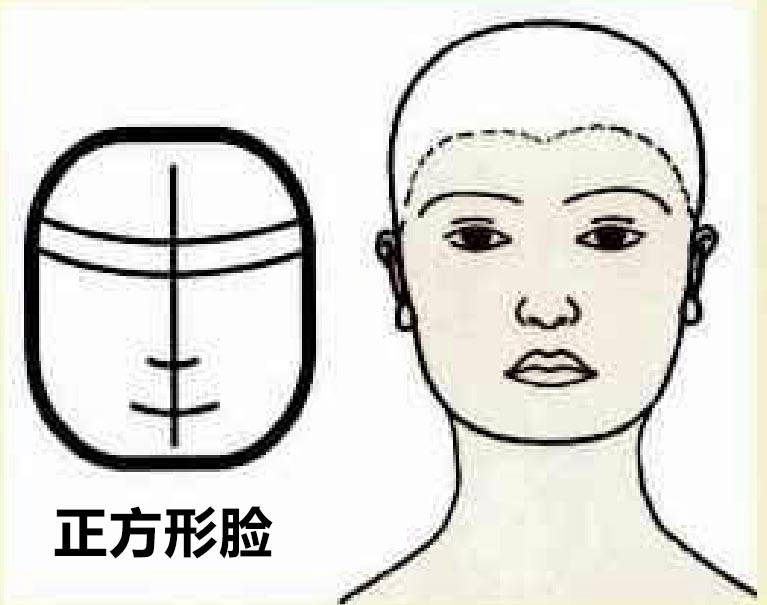

从上面的示意图中 , 我们可以了解到:

在水平方向 , 也即bit line方向 , 不一样储存单元cell之间相距较远并且有绝缘层阻隔 , 可以说在水平方向 , 不一样储存单元cell之间的干扰基本不存在 。

在垂直方向 , 不一样cell之间的距离达到40nm, 比平面NAND的十几nm要大很多 , 所以 , 在垂直方向 , 不一样储存单元cell之间的干扰很小 。

在2D平面NAND中 , 储存单元cell采用的是浮栅结构 , 如下图左 , 电荷存在浮栅导体中 。而在三星V-NAND中 , 储存单元采用的是CTF结构 , 电荷储存在绝缘体中 , 如下图右 。与浮栅结构相比 , CTF结构由于电荷储存在绝缘体中 , 电荷更不容易跑出去 , 所以 , 在某种程度上 , 可以说采用CTF结构的NAND闪存比采用浮栅结构的NAND闪存更加可靠 。

这里还要提一下 , 在当下3D NAND技术中 , 英特尔(Intel)和美光(Micron)发布的3D NAND依旧采用的浮栅结构 , 这里不是要对比Intel/Micron和三星3D NAND优劣 , 我们只是从技术角度分析哦 。Intel/Micron的3D NAND有自己的优化措施 , 还是值得信赖的 。

我们刚才提到的不一样储存单元之间的干扰效应 , 在这里我们看一副对比图:

【看V-NAND有哪些优势 V-NAND优势特点【介绍】】从上图中 , 我们看到 , 与平面NAND闪存相比 , V-NAND储存单元cell的分布区间变窄了33% , 变窄的好处就是减少了读写的错误几率 , 让cell更加可靠 。另外 , V-NAND的储存单元cell之间的干扰下降了84% , 同样 , 不一样储存单元cell之间的干扰减少 , 也可以很大程度上提升NAND的可靠性 。

感兴趣并且预算允许的同学 , 可以买个三星V-NAND固态硬盘玩玩 , 你会很惊艳的!

经验总结扩展阅读

- 三星PS51D6900有HDMI端口吗

- 天润暖气片有哪些种类 天润暖气片分类介绍【详细解析】

- 万国手表型号在哪里看,为什么有些万国手表查不到型号

- 奶粉缺少核苷酸有影响吗,求助英文名!!!

- 男生发白山茶什么意思,关于白山茶的诗句还有它的意思

- 必胜客会员年卡有什么用,必胜客联名会员卡每年都有吗

- 手提储压式干粉灭火器报废年限为,手提式干粉灭火器有效期

- 马赛人平均身高,黑人拥有最强壮的体格,人口密度也大,为什么冷兵器时代没有去征服世界

- 维生素c有什么作用,维生素C有什么作用?

- 打雷玩电脑有影响吗,打雷时玩电脑对电脑有危险吗?